Product Summary

EPF10K50EFC256-3 devices are enhanced versions of FLEX 10K devices. Based on reconfigurable CMOS SRAM elements, the FLEX architecture incorporates all features necessary to implement common gate array megafunctions. With up to 200,000 typical gates, EPF10K50EFC256-3 provide the density, speed, and features to integrate entire systems, including multiple 32-bit buses, into a single device. The ability to reconfigure EPF10K50EFC256-3 enables 100% testing prior to shipment and allows the designer to focus on simulation and design verification. EPF10K50EFC256-3 reconfigurability eliminates inventory management for gate array designs and generation of test vectors for fault coverage.

Parametrics

EPF10K50EFC256-3 absolute maximum ratings: (1)Supply voltage:–0.5-3.6 V;–0.5-4.6V; (2)DC input voltage:–2.0-5.75 V; (3)DC output current, per pin:–25-25 mA; (4)Storage temperature:–65-150°C; (5)Ambient temperature:–65-135 °C.

Features

EPF10K50EFC256-3 features: (1). Embedded programmable logic devices (PLDs), providing system-on-a-programmable-chip (SOPC) integration in a single device; (2).High density; (3).System-level features; (4).Flexible interconnect; (5).Powerful I/O pins;(6).Software design support and automatic place-and-route provided by Altera’s development systems for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800; (7).Flexible package options; (8)Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM).

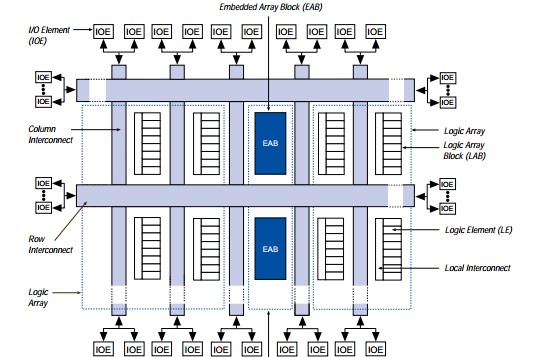

Diagrams

(China (Mainland))

(China (Mainland))